文章目录

- wire线网类型介绍

-

- 一、问题描述

- 二、verilog源码

- 三、仿真结果

wire线网类型介绍

wire线网类型是verilog的一种数据类型,它是一种单向的物理连线。它可以是输入也可以是输出,它与reg寄存器数据类型不同,它不能存储数据,只能用于组合逻辑建模。常用于assign连续赋值语句。另外线网类型数据如果没有信号给它驱动时,它的值为未知X。

一、问题描述

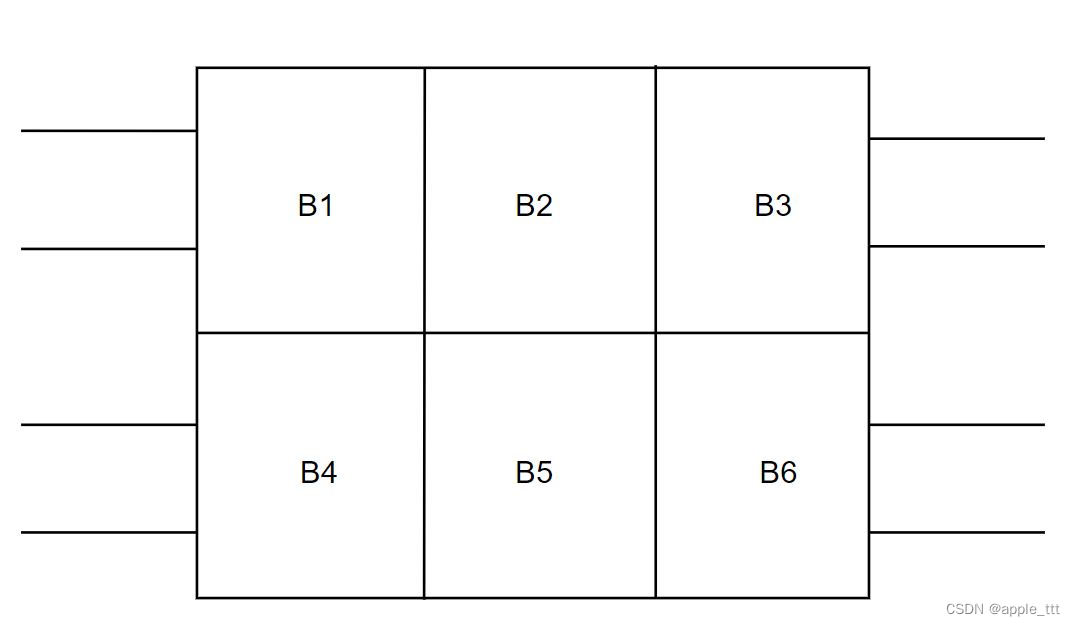

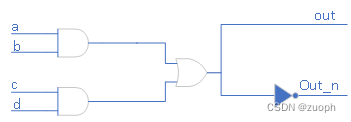

创建一个模块实现内部四个输入通过两个与门输出,然后进入或门,之后分别输出反相和不反相的信号,它由两个与门一个或门再加一个非门组成,内部需要声明三个线网来实现互连,通过wire类型数据将输入和输出连接起来。

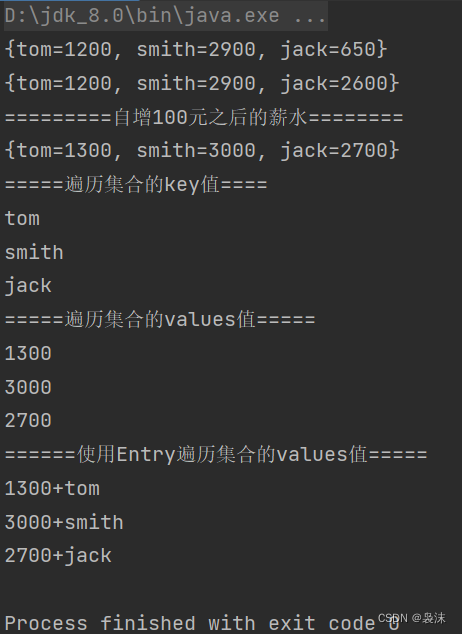

二、verilog源码

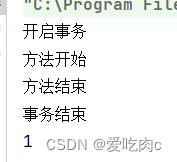

`default_nettype none

module top_module(

input a,

input b,

input c,

input d,

output out,

output out_n );

wire w1, w2, w3;

assig

![[MIT 6.1810]Lab7-networking](https://img-blog.csdnimg.cn/750c65041ddb44c6ad1f11f6679224f4.png)