文章目录

-

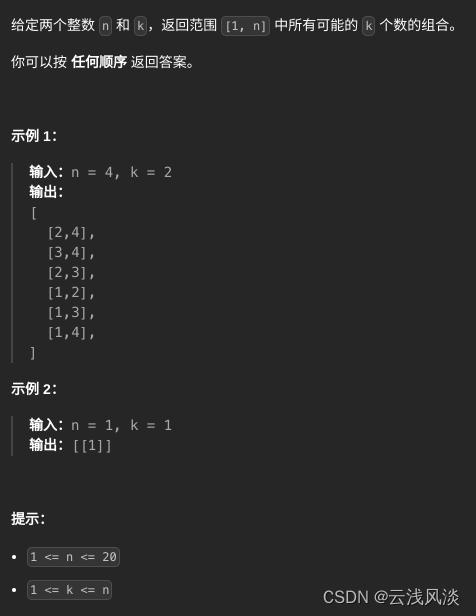

- 一、问题描述

- 二、verilog源码

- 三、仿真结果

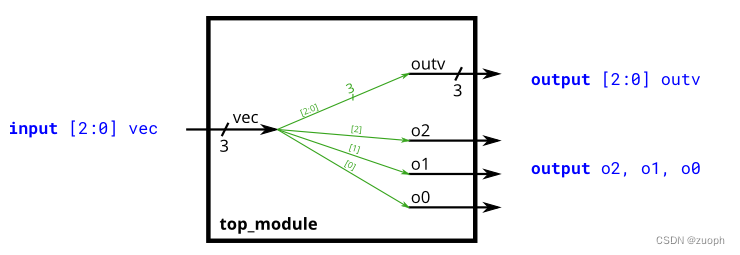

一、问题描述

向量用于使用一个名称对相关信号进行分组,以使其更易于操作。例如,声明一个名为 8 位向量, wire [7:0] w; 该向量在 w 功能上等效于具有 8 个单独的线网(wire w0, w1, w2, w3, w4, w5, w6, w7)。

与C语言的数组定义不同,定义时它的维度放在向量名称前面,选择其中某个数据时和C语言类似。比如:

wire [7:0] datbus;

assign aa = datbus[0];

构建一个具有一个3位输入的电路,然后输出相同的向量,并将其分成三个独立的1位输出。将输出 o0 连接到输入向量的位置o0位置 0、 o1 位置 1 等。

二、verilog源码

module top_module (

input wire [2:0] vec,

output wire [2:0] outv,

output wire o2,

output wire o1,

output wire o0 ); // Module body starts after module declaration

![[人工智能-综述-15]:第九届全球软件大会(南京)有感 -4-大语言模型全流程、全方面提升软件生产效能](https://img-blog.csdnimg.cn/43e3de8f115c4ccba6dccb91391ccee9.png)