1,为什么有触发器?

数字逻辑电路系统包含组合逻辑和时序逻辑。组合逻辑用来实现与状态无关的门电路,比如算法的实现函数,无反馈,无记忆;时序逻辑则主要用来同步电路的各个状态,有反馈,有记忆,如触发器,寄存器。 组合逻辑计算出来的值由时序逻辑保存下来,经过同步时钟(Clock)来控制逻辑值的传递。

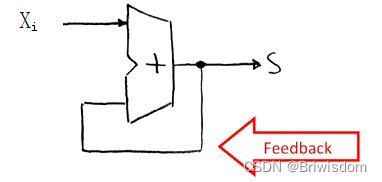

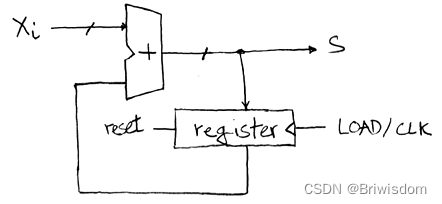

比如实现一个如下的累加功能电路设计,如果不用触发器,则无法存储s的中间值,无法控制状态转换。

int s=0;

for(int i = 0; i<10; i++)

{

s = s + X[i];

}

2,触发器,锁存器的电路结构

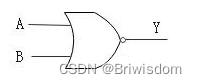

或非门

输入A, B, 输出 Y,

或非门即: A和B只要有一个为1,则Y为0; A和B全为0,则Y为1;

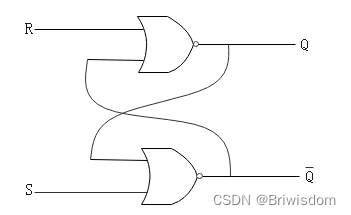

触发器

把两个或非门连起来,能够稳定

保存电路状态的电路称为触发器,如下是一个R-S触发器,有两个输入端S(set), R(reset), 2个输出端Q 和 ~Q,约定S和R不会同时为1。

状态表如下,R-S触发器的最大特点是它能记住2个输入端的状态。当把2个输入端都置0时候,能记住上一次的状态。计算机中的寄存器,内存最基础的组成单元就是触发器。

| S | R | Q | ~Q |

| 1 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 0 | Q | ~Q |

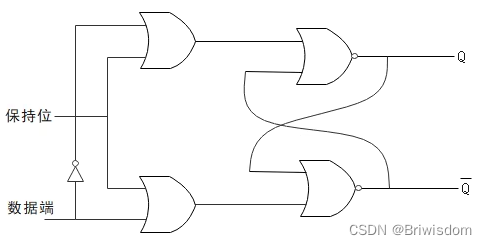

锁存器

上面触发器R,S同时是数据输入端和控制端,有点耦合,所以可以优化一下电路图,把数据和控制分开。我们试着增加一个具有控制功能的【保持位】,它能决定当前电路状态是否被“记住”。当保持位为1时,数据输入的值被记住,当保持位为0时候,数据输入位为任何值都不影响电路的状态。增加了保持位的这个电路称为D(data)型触发器。原来的R和S的状态实际是互斥的,所以用一个非门替换,如下图。

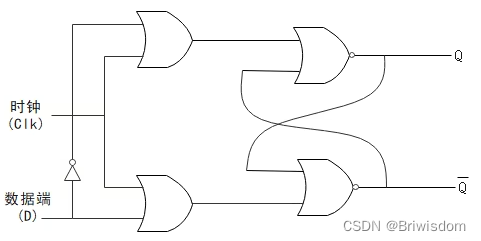

通常,保持位就是电路时序中的时钟信号(clock),这种用时钟控制的D触发器也称作锁存器,顾名思义,数据存储进去就像被锁住了一样。

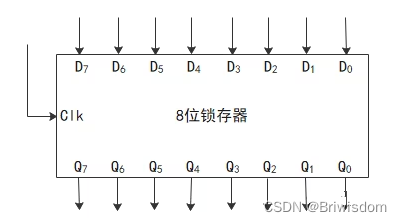

把8个锁存器的时钟端接在一起,引入输入端和输出端,就构成了一个8位的锁存器。

参考:一文了解硬件加法器、触发器、锁存器-电子工程专辑

![[论文笔记]SimCSE](https://img-blog.csdnimg.cn/img_convert/23ca7438cadf266f0be5fba1e0cb7689.png)

![[python] pytest](https://img-blog.csdnimg.cn/c3021b5780444e82b705ab8261b22a2c.png)

![[补题记录] Atcoder Beginner Contest 294(E)](https://img-blog.csdnimg.cn/82df4c726b2242879d6ebe6ef1ab80ea.png)