一、 选择题:(共20分,每小题2分)

1、逻辑函数的所有最小项之和等于多少?

A. 0 B. 1

C. 0或1 D. 任意值

2、与非门的多余输入端应如何处理?

A. 接高电平 B. 接地

C. 接地或接高电平都可以 D. 接输出

3、既可进行数字信号传输又可进行模拟信号传输的器件为哪个?

A. 三态门 B. 锁存器

C. CMOS传输门 D. 触发器

4、可以将输出端直接并联实现“线与”逻辑的门电路是哪个?

A. 所有结构的门电路 B. 漏极开路的门电路

C. 互补输出结构的CMOS门电路 D. 哪个也不可以

5、输出具有高阻抗状态的电路是?

A. 漏极开路的门电路 B.传输门

C. 互补输出结构的CMOS门电路 D.三态门电路

6、为了把串行输入的数据转换为并行输出的数据,可以使用以下哪种电路?

A.寄存器 B. 计数器

C. 存储器 D. 移位寄存器

7、用5个触发器,最多可构成多少进制的计数器?

A. 5进制 B. 10进制

C. 32进制 D. 25进制

8、某存储器有10根地址线,有8根平行数据线,则该存储器的最大存储容量为多少?

A. 1K×8 B. 1M×8

C. 10×8 D. 1 0×64

9、以下各种A/D转换器电路类型中,转换时间与输入电压大小有关的是哪种?

A. 逐次逼近型 B. 并联比较型

C. 双积分型 D. 无法确定

10、关于FPGA,你认为:

A. 只能实现组合逻辑电路 B. 只能实现时序逻辑电路

C. 只是一个软件程序,不能实现任何电路 D. 组合、时序逻辑电路,均能实现

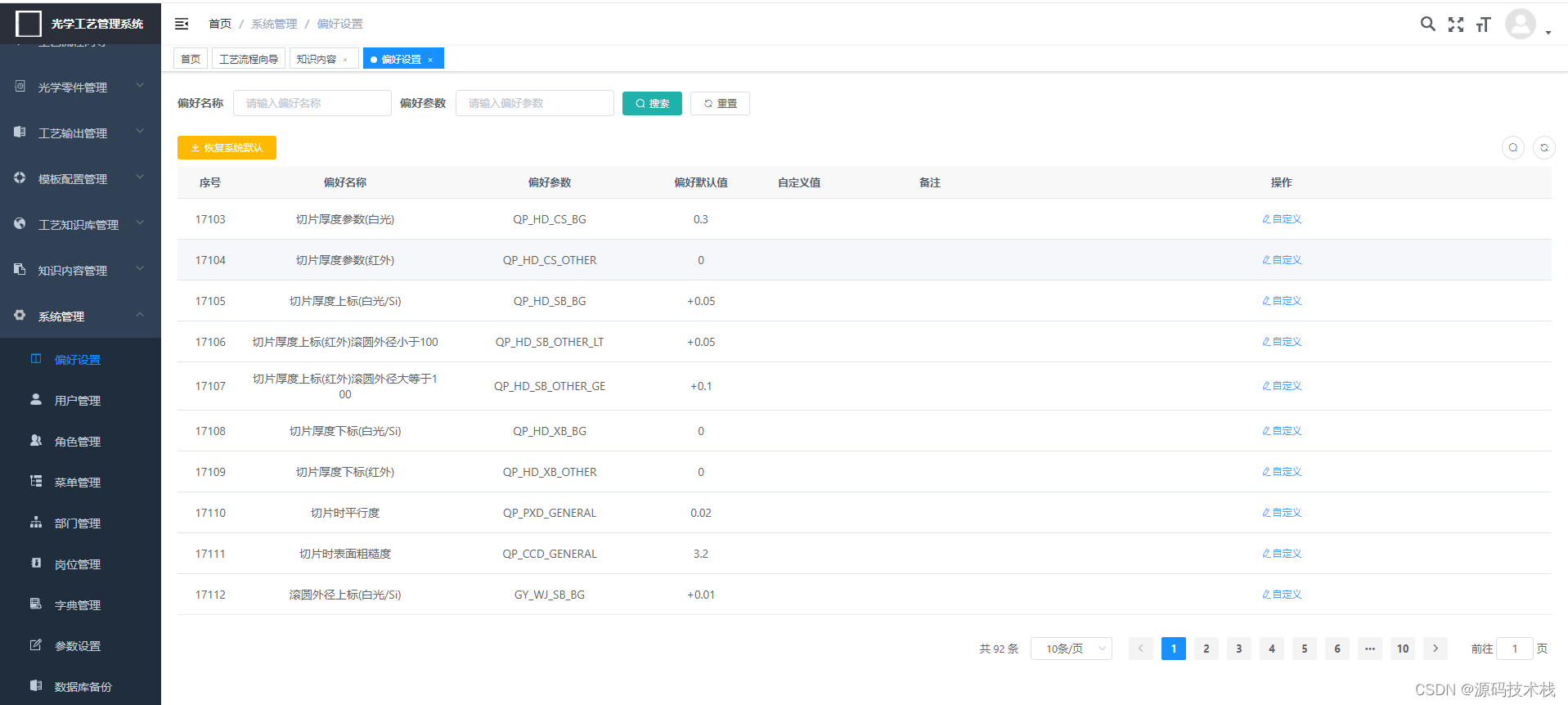

二、用八选一数据选择器接成的多功能组合逻辑电路如图所示。G1、G0为功能选择输入信号,X、Z为输入逻辑变量,F为输出信号。试分析该电路在G1G0取不同选择信号时,可获得哪几种逻辑功能。 (15分)

三、设计一个1位二进制全减器电路。输入为被减数、减数和来自低位的借位信号;输出为相减之差、以及向高位的借位信号。要求用3线-8线译码器74HC138和必要的门电路来实现。

3线-8线译码器74HC138的符号如图所示。其输出与输入的关系为Yi’= mi’ (10分)

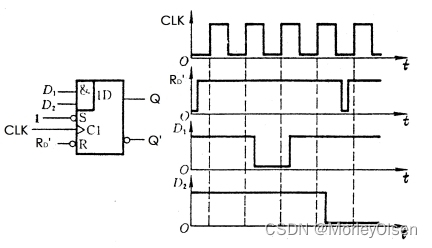

四、已知边沿触发的D触发器各输入端的电压波形如图所示,试画出Q、Q’端对应的电压波形。

(在答题纸上,要画出CLK、RD’、D1、D2、Q、Q’的对应波形) (10分)

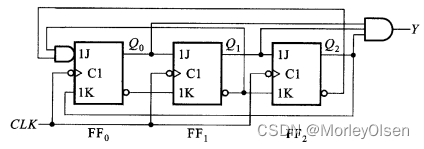

五、时序电路的分析。写出图示电路的驱动方程、状态方程和输出方程,画出电路的状态转换图。检查电路能否自启动,并说明电路的逻辑功能。 (15分)

六、试用4位同步二进制计数器74LS161接成十二进制计数器,标出输入、输出端,列出有效状态的状态转换图。可以附加必要的门电路。 74LS161的功能表和逻辑符号如下所示。 (10分)

七、用Verilog HDL对某种触发器的描述如下: (5分)

module flip-flop(data,clk,reset,q);

input data,clk,reset; ………..⑴

output q;

reg q;

always@(posedge clk) …………⑵

if (~reset) begin ………….⑶

q<=1’b0; ………….⑷

end else begin ………….⑸

q<=data; ………….⑹

end

endmodule

1. 以上模块中,分别简要说明⑴-⑹的作用;

2. 该模块描述的是什么类型的触发器?

3. 是在时钟脉冲的上升沿,还是下降沿进行触发?

4. 是同步复位,还是异步复位?

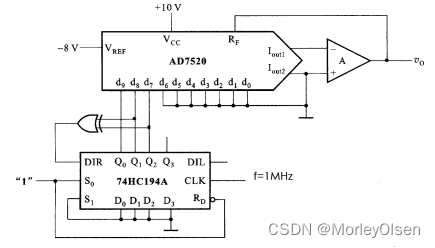

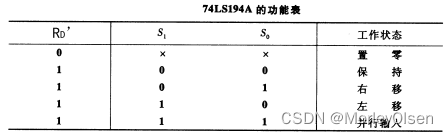

八、下图中,AD7520是10位输入的倒T型电阻网络D/A转换器,参考电压VREF=–8V。74HC194A是四位双向移位寄存器,其功能表如下表所示,设它的初始状态为Q0Q1Q2Q3=1000。DIR和 DIL分别为右移数据输入端和左移数据输入端。时钟频率为1MHz。 (15分)

⑴ 74HC194A的时钟CLK的周期为多少?

⑵ 根据图中情况,写出输出电压的表达式。(vo与Q0、Q1、Q2的关系式)

⑶ 分析74HC194A的工作情况,列出Q0Q1Q2Q3的状态转换表,并计算对应的D/A转换器的输出电压数值。

⑷ 画出输出电压波形图(标出横坐标、纵坐标的数值及单位)。

⑸ 输出电压波形的周期是多少?