随着社会智能化程度越来越高,数字化转型全面加速,市场对电子系统的精确度要求也越来越高!

电子系统,如何保障运行精确度?

一般情况下需要用到“时钟信号”,用来同步各种组件的操作体系对应的数字逻辑,调节数字状态机的顺序。

时钟信号的目的是确保关键的时间参数都在允许的范围内,比如设置和保持时间、传播延迟等。在通信系统中,时钟信号调节同步数据传输的连接速度。

对现代电子系统来讲,时钟信号可能被需求为多个不同频率或者不同输出格式的单一频率的多个输出。

当然,严格控制相位和频率的关系,与外部同步频率源、减少电磁干扰的调制和冗余开关也是系统所需。

电子系统获取时钟信号的方式:

1.晶体和振荡器

晶振是指产生谐振频率的电子元件,常用的是石英晶体谐振器和陶瓷谐振器。封装有插件和贴片两种方式。主要作用是给电路提供频率信号,具有稳定,抗干扰性能良好的特点,被广泛应用于各种电子产品中。

石英晶体谐振器是一种从石英晶体上按一定方位切下薄片,然后将薄片添加IC组成振荡电路并封装起来的元件,简称为石英晶体、晶体或晶振。一般用金属外壳封装,也有用玻璃壳、陶瓷或塑料封装的。封装以贴片为主。

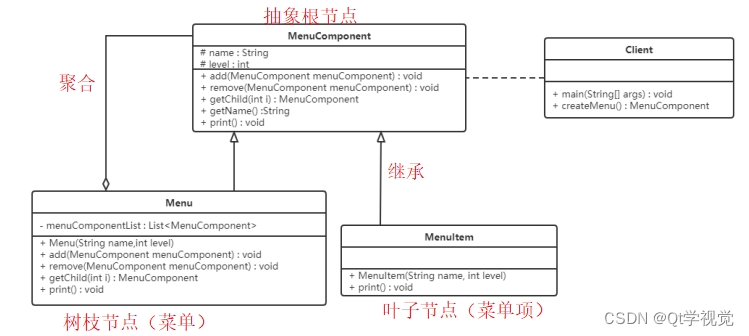

2.PLL时钟芯片

通常情况下,大多数电子设备正常工作需要外部的输入信号与内部的振荡信号同步。利用锁相环路可以实现同步。

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因为锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压可以保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

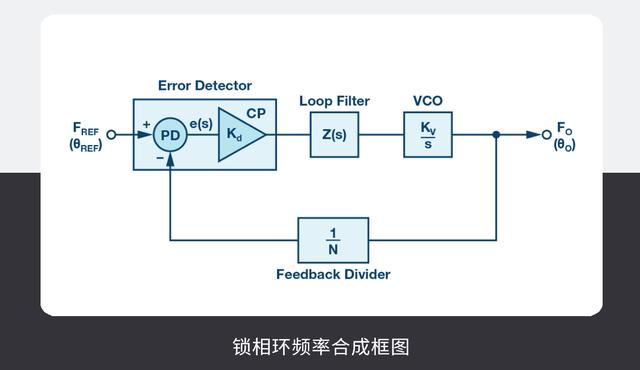

锁相环通常由鉴相器(PD,Phase Detector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator)三部分组成。

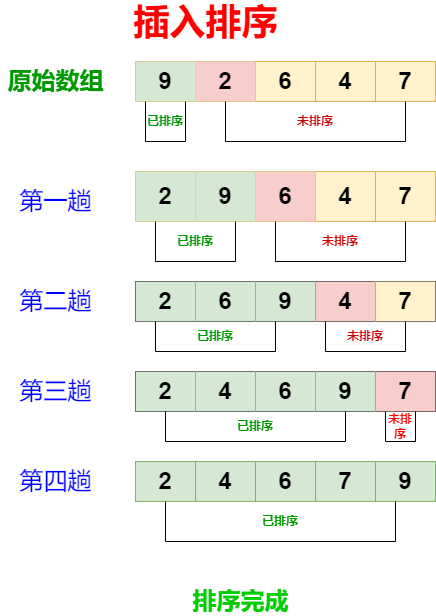

如果想要获得多频率、高稳定的振荡信号输出,则需要利用PLL、 倍频、分频等频率合成技术。下面是锁相环频率合成框图,当图中的N小于1时,为分频电路;N大于1时,为倍频电路。

传统晶体/振荡器的劣势:

现在的电子系统复杂程度越来越高,当一个电子产品需求多个晶体/谐振器时,如果仍选择传统的晶体或者振荡器就会出现诸多限制:

1.成本:

当一个电子产品需求多个晶体/谐振器, 特别是需求不同频率时,一个可以输出多路时钟信号的时钟发生器的成本比几个晶体/谐振器有优势。

2.可靠性:

由于产品特性,晶体/谐振器的失效率比硅芯片高很多。频率越高, 失效率越高,会降低电子产品的可靠性。

集成度更高的PLL时钟芯片可以提高电子产品的可靠性, 降低产品的返修率。

3.可适用性:

高于50MHz的高频晶体由于需要使用高阶泛音晶体, 生产工艺复杂,价格昂贵。

PLL时钟芯片只需要一个低频晶体或一个可用的时钟参考就能产生多路高频高性能的时钟信号。

4.Aging:

晶振容易老化。由于晶体材料和晶体表面的杂质以及晶体材料之间的机械应力, 晶体会以±2ppm到±5ppm的误差变化。因供应商不同,每种晶体的老化情况也有所不同。但都可能会导致全系统缓慢的退化。

PLL时钟芯片可以在设备的整个生命周期中都保持其准确性。

5.存储管理:

管理进入生产系统的每个设备的材料库存、需求和预测计划,是采购团队现存的难题之一。特别是对于有多个产品的平台而言, 需求的晶体/谐振器数量更多,管理这些以及其背后的供应链所带来的问题更加繁琐。

PLL时钟芯片具备高集成度,可以解决多料号的问题,便于存储管理。