名称:基于DE0开发板的交通灯十字路口红绿灯

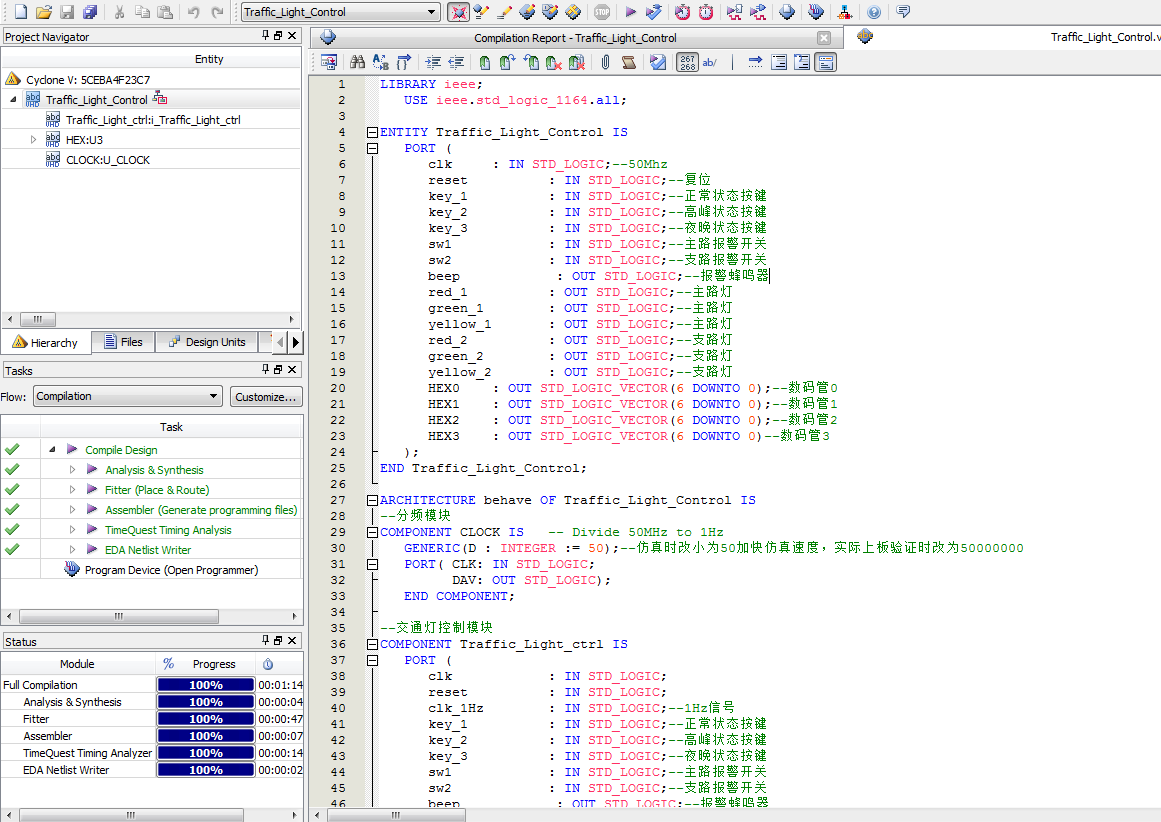

软件:Quartus

语言:VHDL

要求:

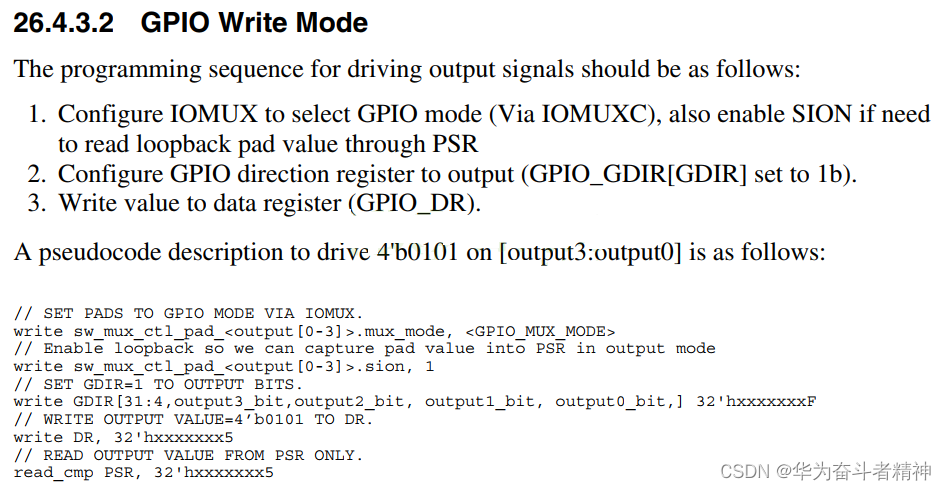

设计一个十字路口交通信号灯的控制电路。分为两种情况,正常状态和报警状态。

1.正常状态:要求红、绿灯按一定的规律亮和灭,并在亮灯期间进行倒计时,且将运行时间用数码管显示出来。

绿灯亮时,为该车道允许通行信号,红灯亮时,为该车道禁止通行信号。

要求主干道每次通行时间为 60秒,支干道每次通行时间为 30 秒。

每次变换运行车道前绿灯闪烁,持续时间为 5 秒。

即车道要由 X转换为 Y时,X在通行时间只剩下 5 秒钟时,绿灯闪烁显示, Y仍为红灯。

2.报警状态:亮黄灯,蜂鸣器响起。(蜂鸣器高电平触发)

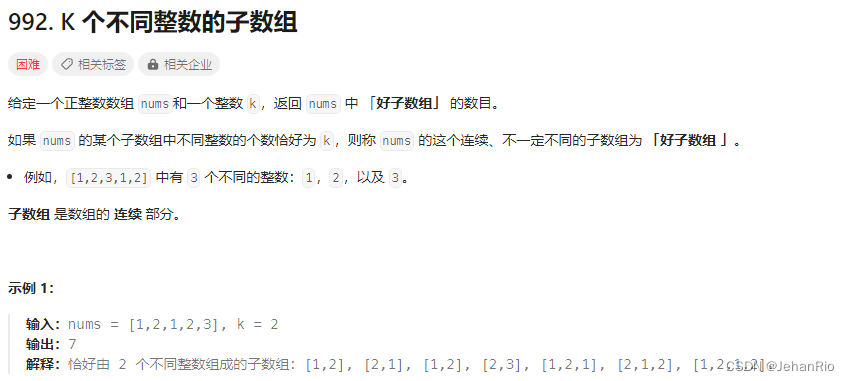

外接键盘:三种模式的切换:高峰,正常,夜晚

高峰:x:绿灯 35S 红灯25S;y:绿灯 25S 红灯35S。

夜晚:x:绿灯 45S 红灯45S;y:绿灯 45S红灯45S

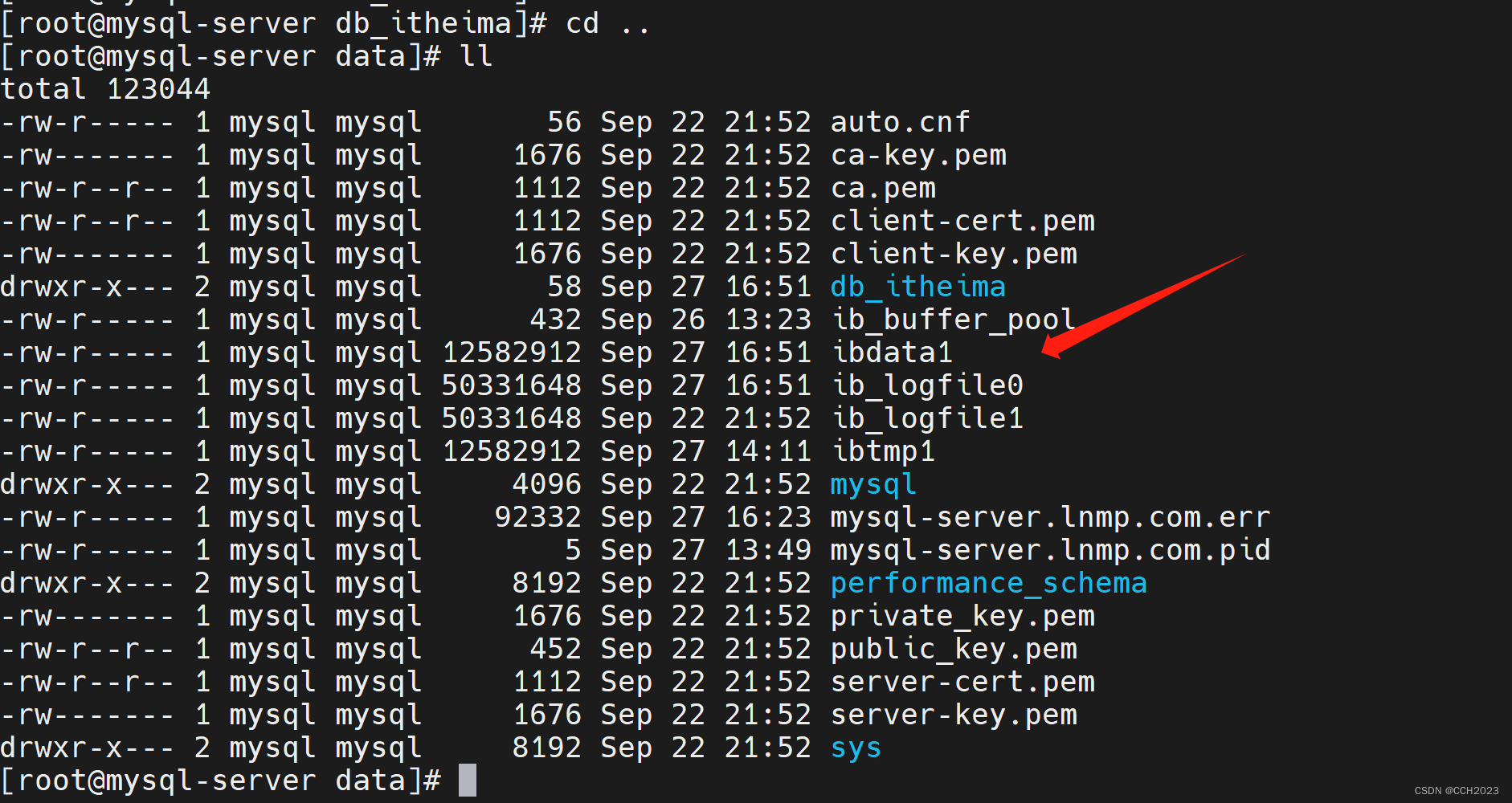

本代码已在DE0-CV开发板验证,板子资料如下:

FPGA_DE0-CV.pdf

代码下载:DE0开发板交通灯十字路口红绿灯_Verilog/VHDL资源下载

代码网:hdlcode.com

部分代码展示

LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY Traffic_Light_Control IS PORT ( clk : IN STD_LOGIC;--50Mhz reset : IN STD_LOGIC;--复位 key_1 : IN STD_LOGIC;--正常状态按键 key_2 : IN STD_LOGIC;--高峰状态按键 key_3 : IN STD_LOGIC;--夜晚状态按键 sw1 : IN STD_LOGIC;--主路报警开关 sw2 : IN STD_LOGIC;--支路报警开关 beep : OUT STD_LOGIC;--报警蜂鸣器 red_1 : OUT STD_LOGIC;--主路灯 green_1 : OUT STD_LOGIC;--主路灯 yellow_1 : OUT STD_LOGIC;--主路灯 red_2 : OUT STD_LOGIC;--支路灯 green_2 : OUT STD_LOGIC;--支路灯 yellow_2 : OUT STD_LOGIC;--支路灯 HEX0 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);--数码管0 HEX1 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);--数码管1 HEX2 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);--数码管2 HEX3 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0)--数码管3 ); END Traffic_Light_Control; ARCHITECTURE behave OF Traffic_Light_Control IS --分频模块 COMPONENT CLOCK IS-- Divide 50MHz to 1Hz GENERIC(D : INTEGER := 50000000);--仿真时改小为50加快仿真速度,实际上板验证时改为50000000 PORT(CLK: IN STD_LOGIC; DAV: OUT STD_LOGIC); END COMPONENT; --交通灯控制模块 COMPONENT Traffic_Light_ctrl IS PORT ( clk : IN STD_LOGIC; reset : IN STD_LOGIC; clk_1Hz : IN STD_LOGIC;--1Hz信号 key_1 : IN STD_LOGIC;--正常状态按键 key_2 : IN STD_LOGIC;--高峰状态按键 key_3 : IN STD_LOGIC;--夜晚状态按键 sw1 : IN STD_LOGIC;--主路报警开关 sw2 : IN STD_LOGIC;--支路报警开关 beep : OUT STD_LOGIC;--报警蜂鸣器 red_1 : OUT STD_LOGIC;--主路灯 green_1 : OUT STD_LOGIC;--主路灯 yellow_1 : OUT STD_LOGIC;--主路灯 red_2 : OUT STD_LOGIC;--支路灯 green_2 : OUT STD_LOGIC;--支路灯 yellow_2 : OUT STD_LOGIC;--支路灯 main_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--主路倒计时 branch_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--支路倒计时 ); END COMPONENT; --显示模块 COMPONENT HEX IS PORT ( clk : IN STD_LOGIC; SMG_1 : IN STD_LOGIC_VECTOR(7 DOWNTO 0); SMG_2 : IN STD_LOGIC_VECTOR(7 DOWNTO 0); HEX0 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0); HEX1 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0); HEX2 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0); HEX3 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0) ); END COMPONENT; SIGNAL clk_1 : STD_LOGIC; SIGNAL main_time : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL branch_time : STD_LOGIC_VECTOR(7 DOWNTO 0);

设计文档(文档可下载):

设计文档.doc

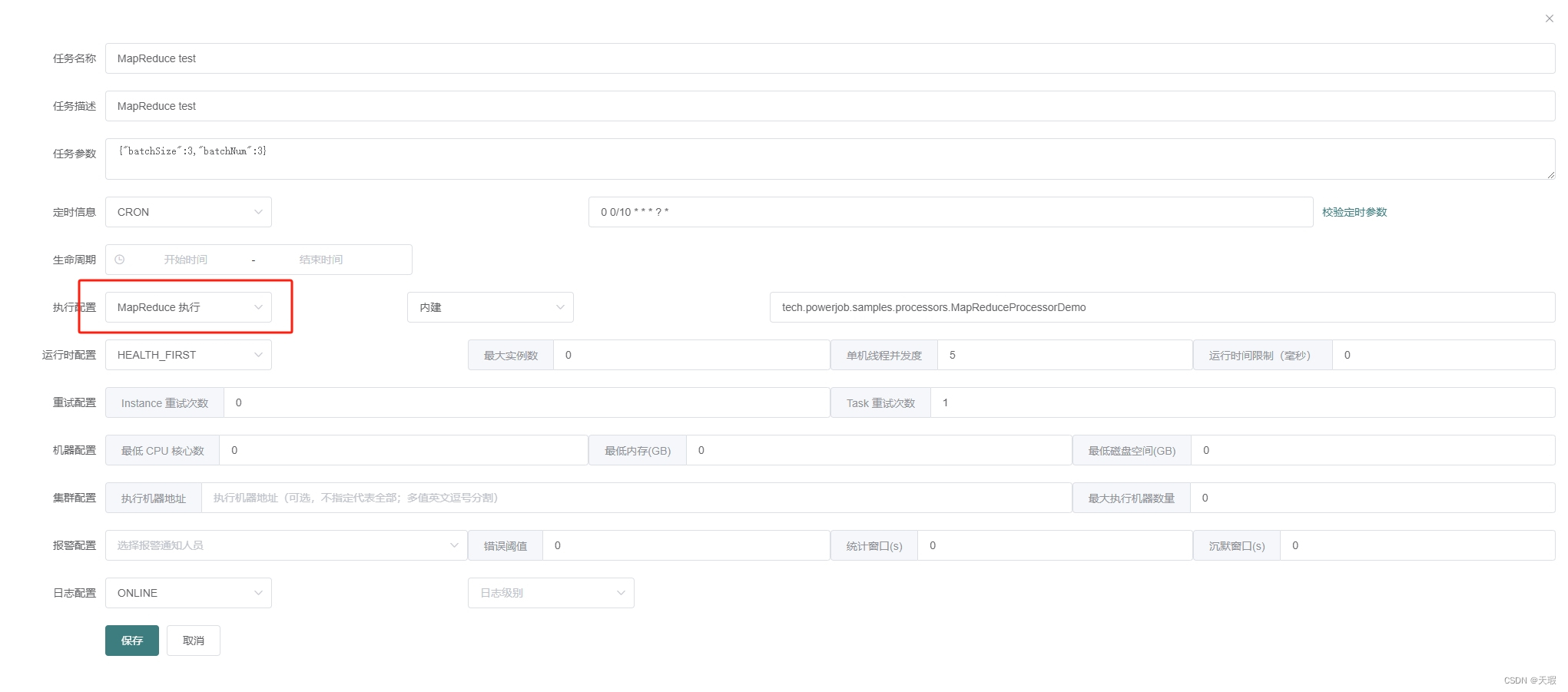

1. 工程文件

2. 程序文件

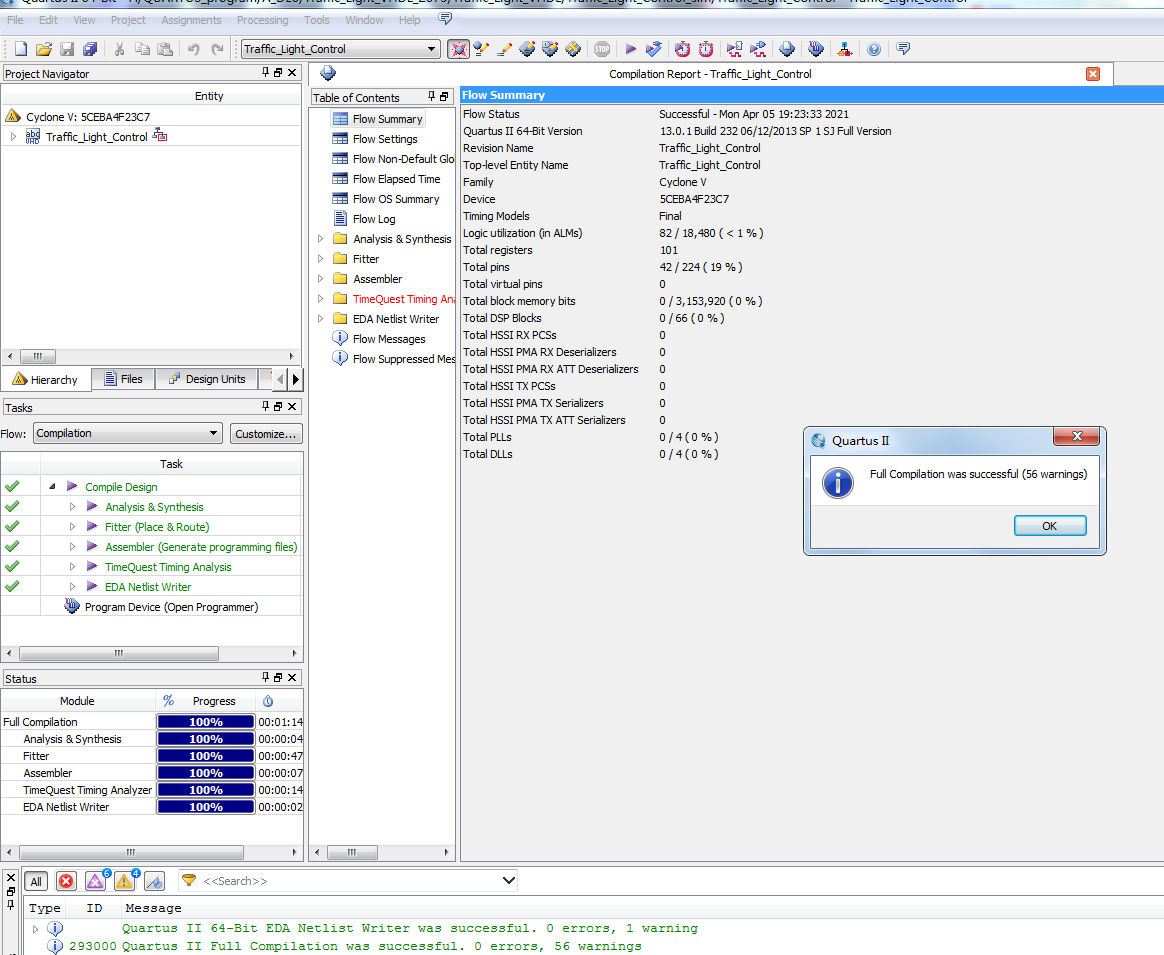

3. 程序编译

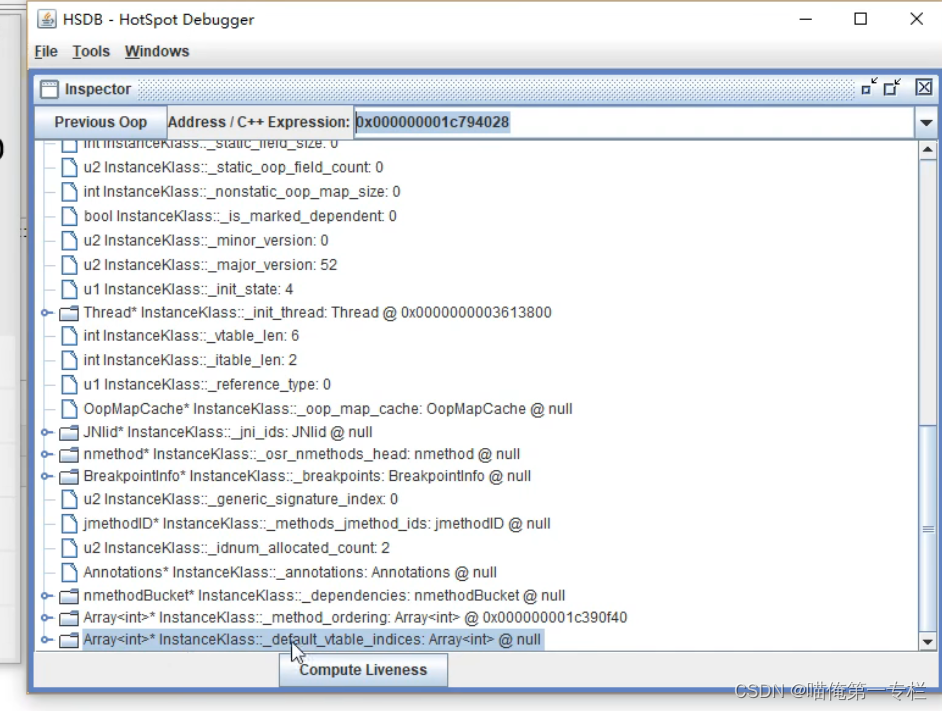

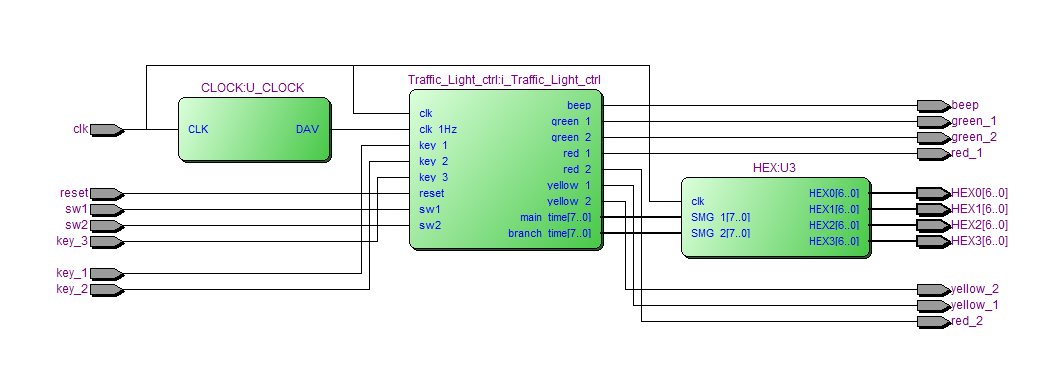

4. RTL图

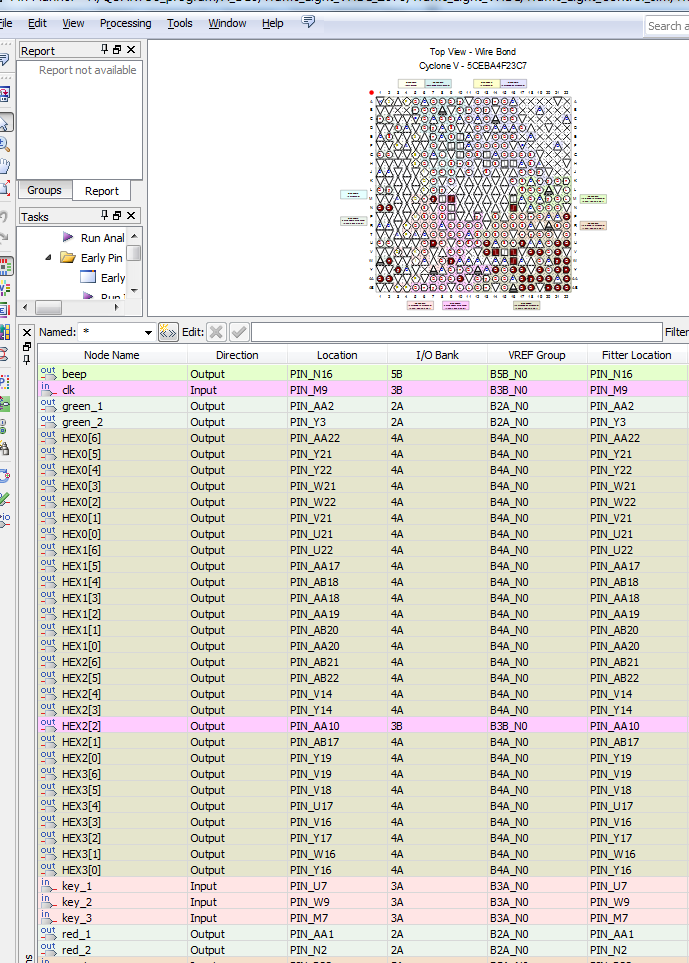

5. 管脚分配

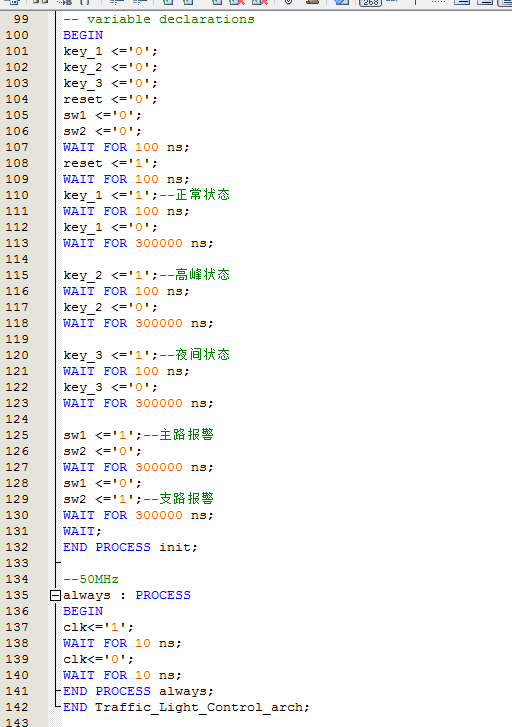

6. Testbench

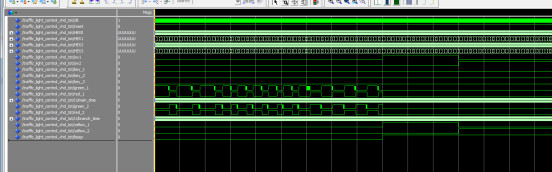

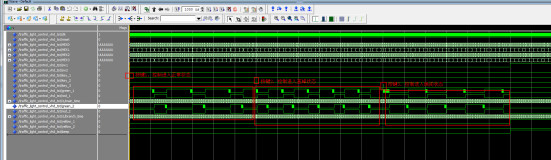

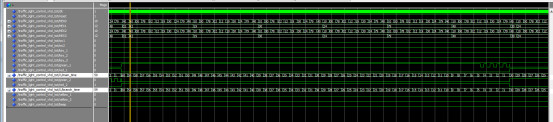

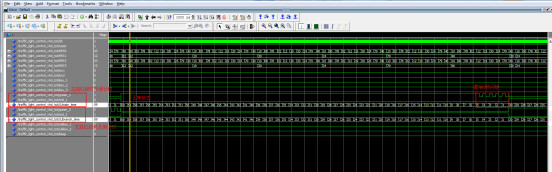

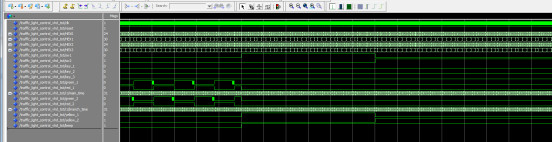

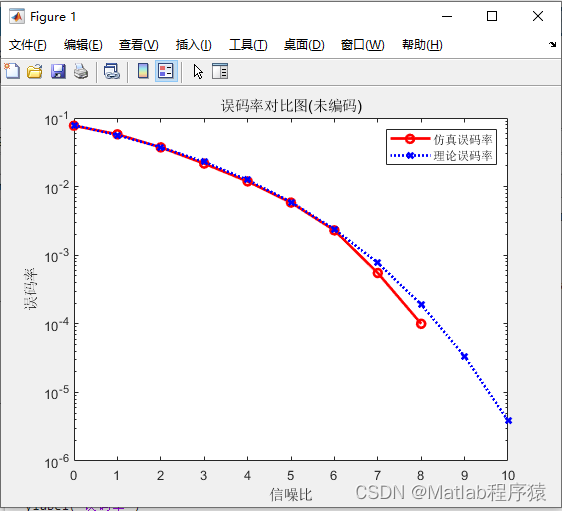

7. 仿真图