嵌入式开发工程师曾使用光电耦合器进行I2C隔离。这些电路有些复杂,对总线电容敏感,并且速度有限。它们也与具有标准CMOS输入电平的高速数字隔离器不兼容。

该嵌入式开发工程师思想展示了如何将标准的高速数字隔离器转换为双向I2C隔离器。除了与数字隔离器兼容之外,该电路比以前发布的解决方案更简单,对总线电容完全不敏感,并且可以轻松支持标准的400KHz最大I2C总线速率。

标准I2C SDA和SCL信号由漏极驱动器驱动。在所有情况下,SDA都可以由总线上的任何设备驱动,以便SDA总线将信息从I2C主设备传递到从设备,并将信息从从设备传递到主设备。即,数据传输是双向的。在某些情况下,SCL仅具有I2Cmaster的驱动程序。

但是,在许多情况下,例如多个I2C主设备,或者如果从设备需要在检索数据时将其保持为低电平来扩展SCL,则SCL线也必须是双向的。

对于需要双向传输的电线,如果插入数字隔离器,则存在几个问题;隔离器必须开漏,并且可能发生闩锁情况。例如,如果A侧驱动器拉低,则隔离器A在B侧拉低。

这会导致隔离器B在A侧拉低,并且两个隔离器都拉低时电路锁存。通过将肖特基二极管与隔离器输出串联可以很容易地解决开漏问题,但是闭锁问题要难得多。

解决该问题的先前尝试是使用光耦合器输入固有的二极管和附加电路来避免闭锁情况。这些方法中的一些对总线电容敏感。

由于光耦合器的响应较慢,它们往往会变慢。最后,当使用具有标准CMOS输入电平的高速数字隔离器时,使用光耦合器的二极管输入的电路技巧就不再适用。

使用数字隔离器

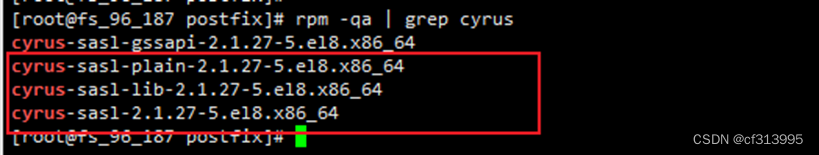

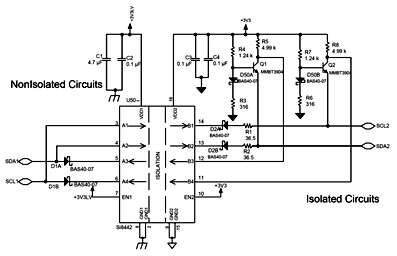

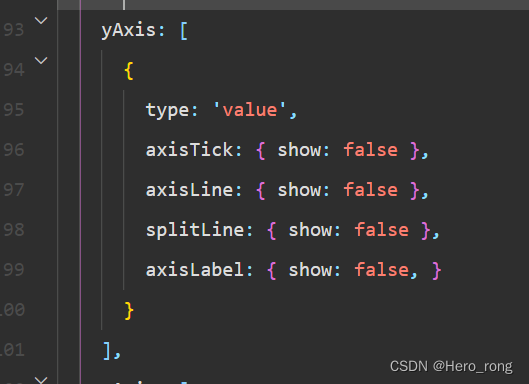

的电路下图1显示了使用Silicon Laboratories,Inc.的Si8442高速隔离器的完整电路。该电路在SCL和SDA线上假设有1K上拉电阻。可以很容易地针对其他总线上拉电阻进行调整。该电路已经过SiliconLaboratories,Inc. C8051Fxxx系列MCU的测试,总线速度约为300KHz,包括需要SCL时钟拉伸的总线事务。

图1:二极管D1A,B和D2A,b将Si8442的推挽输出转换为漏极开路。

通过使用比较器检测非隔离侧(A侧)是否引起隔离侧(B侧)的低电平,解决了上述闩锁问题。晶体管Q1和Q2充当比较器。如果B侧的低电平是由A侧的低电平引起的,则Q1或Q2将不会导通,这是因为二极管D2A,B和R1或R2两端的压降,并且该低电平不会传播回A侧,从而破坏了锁存条件。

如果B侧的低电平是由B侧的漏极开路驱动器引起的,则Q1和Q2确实会导通,并且该低电平会传播。请注意,比较器电路仅需在一侧使用,并且可以在A侧或B侧使用。A侧的电压电平完全符合I2C要求,没有比较器电路的一侧无需特殊考虑。

对于B侧,使用比较器电路时,隔离器的输出不应打开比较器,但漏极开路驱动器必须打开比较器。比较器的阈值由分压器R3,R4和R6,R7设置。二极管D3A,B提供温度补偿以匹配二极管D2A,B。

根据所示的组件值,比较器阈值约为0.28V。肖特基钳位下拉至大约0.5V,开漏驱动器通常下拉至0.1V,因此比较器阈值很好地居于这些值之间。

如果总线上拉电阻不是1K,则Vdd电压不是3.3V,或者带有比较器的那一侧的驱动器不能拉到0.2V以下,则需要调整电路。必须将隔离器的下拉电阻(由二极管D2和R1或R2确定)调整为与连接到B侧总线的设备的逻辑低电平兼容。

比较器阈值由D3(跟踪D2)和分压器R3 / R4或R6 / R7设置。将比较器阈值调整为隔离器电路的下拉和B侧I2C总线上的其他I2C电路的下拉之间的中间位置。

电路性能

隔离电路引入的从A面(非隔离面)到B面(隔离面)的传播延迟对于上升沿和下降沿均可以忽略不计(<50nsec)。这是因为在这个方向上,比较器不在路径中并且不会引入延迟。

对于下降沿,随着晶体管开启,延迟约为50nsec。对于上升沿,由于晶体管关闭,会有大约250nsec的延迟。还要注意,在这种情况下,输入波形的最终上升被延迟了,因此,当波形超过典型的1V CMOS逻辑阈值时,偏斜很小。

该电路引入的增加的延迟与I2C或SMBus操作兼容,速度高达400KHz。因此,与传统实现相比,使用数字隔离器进行I2C隔离为嵌入式开发工程师带来了许多好处。

![[架构之路-222]:邮件服务与协议:POS3和SMTP](https://img-blog.csdnimg.cn/4ba33408e43946d5b1de5b08084c1717.png)