创龙TL6678F开发板官方Demo:SRIO_AD9613 实现了FPGA和DSP之间的SRIO通信, SRIO的速率为5Gbps. 在FPGA端, srio_gen_2 模块的参考时钟为 125MHz. 而Demo: udp_10g_echo 实现了10G以太网通信, ten_gig_eth_pcs_pma模块的参考时钟为156.25 MHz. 两者共用一个 cdcm61002, 且两个参考时钟不能分别设置.

为了在此开发板上同时实现10G以太网和SRIO通信, 需要将SRIO的参考时钟改为156.25MHz(10G以太网参考时钟只能取156.25MHz, 而srio_gen_2线速率改为3.125Gbps时, 支持125MHz和156.25MHz两种参考时钟频率).

本文介绍了如何在创龙TL6678F开发板上实现FPGA与DSP之间 SRIO(3.125Gbps, 4x)通信.

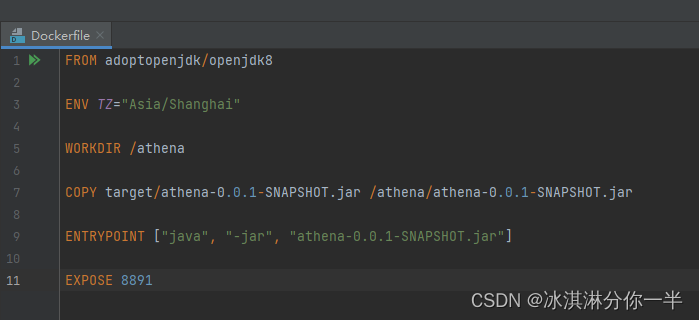

FPGA工程

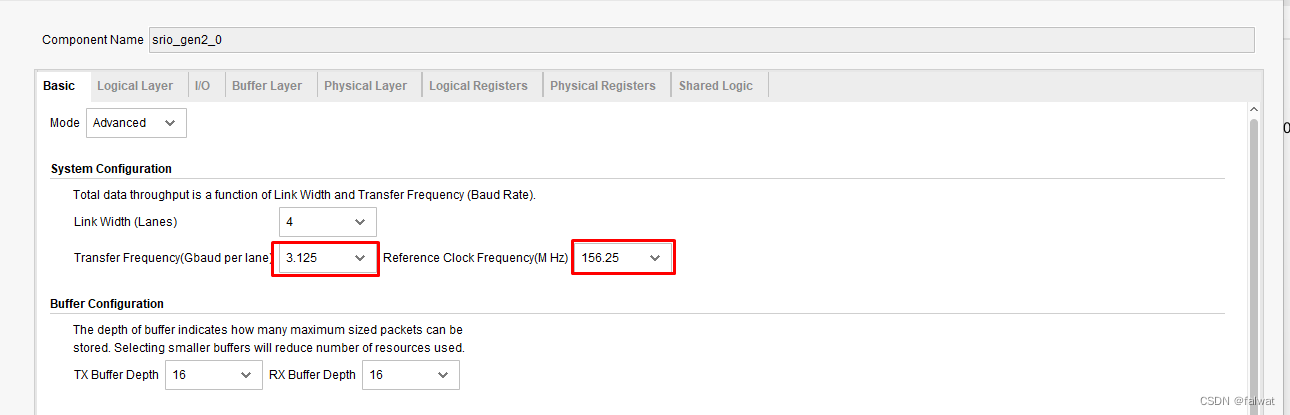

- 打开 fmc_ad9613_srio 工程, 将 srio_gen_2 模块的 Transfer Frequency 改为 3.125, Reference Clock Frequency 改为 156.25.

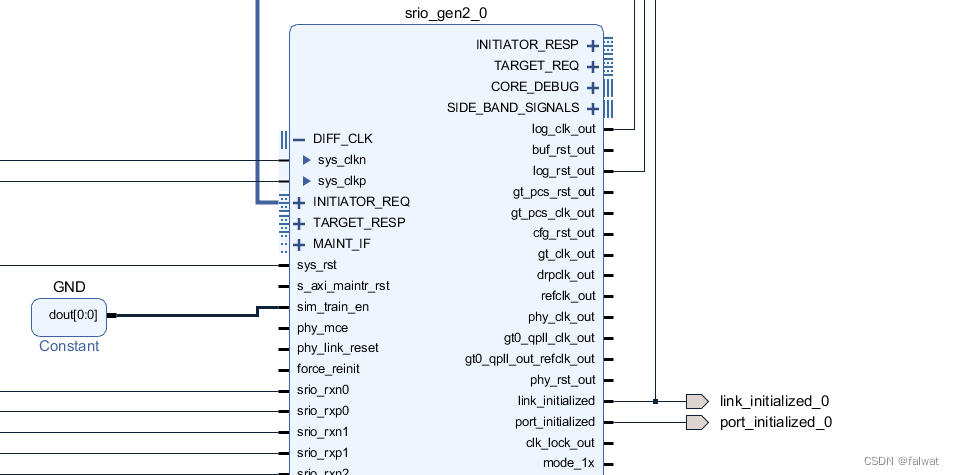

- 为了确认SRIO链路是否连接成功, 将 模块的 link_initialized 和 port_initialized端口引出, 并输出到 SOM-6678F子卡的两个LED上. 约束文件中添加:

- 为了确认SRIO链路是否连接成功, 将 模块的 link_initialized 和 port_initialized端口引出, 并输出到 SOM-6678F子卡的两个LED上. 约束文件中添加:

# user led on som

set_property PACKAGE_PIN AE2 [get_ports user_led1]

set_property PACKAGE_PIN AE3 [get_ports user_led2]

set_property IOSTANDARD LVCMOS15 [get_ports user_led1]

set_property IOSTANDARD LVCMOS15 [get_ports user_led2]

- 综合, 实现并生成bit流文件和bin文件

- 上电烧写FPGA的 PROM.

DSP工程

- 打开 CCS, 并导入 srio_fft 工程

- 修改 srio_fft.c文件.

- 修改 SRIO_SERDES_CFGPLL寄存器的 MPY为 00110010b(12.5x), DSP 的 SRIO参考时钟为 250MHz, 250 ∗ 12.5 = 3125 M H z 250*12.5=3125MHz 250∗12.5=3125MHz

CSL_BootCfgSetSRIOSERDESConfigPLL (0x0065);- 修改 SRIO_SERDES_CFGRX[n] 和 SRIO_SERDES_CFGTX[n] 寄存器的 RATE 为10b(ratescale=1.0), 即每个PLL时钟采集一个数据样本.

for(i = 0; i <= 3; i++) CSL_BootCfgSetSRIOSERDESRxConfig(i, 0x004684a5); for(i = 0; i <= 3; i++) CSL_BootCfgSetSRIOSERDESTxConfig(i, 0x001c8fa5);- 编译并在开发板上调试, 开发板上的两个蓝灯亮, 说明链路初始化和端口初始化完成.

关于DSP SRIO寄存器的详细说明, 请参考: KeyStone Architecture Serial Rapid IO (SRIO)-SPRUGW1B 文档.