华为verilog编程规范是坊间流传出来华为内部的资料,其贴合实际工作需要,是非常宝贵的资料,希望大家善存。至于其介绍,在此不再赘述,大家可看下图详细了解,感兴趣的可私信领取《Verilog代码规范笔记_华为》。

…………

一 共 10 页

想获得完整版《Verilog代码规范笔记_华为》的小伙伴赶快私信获取!

另外,今天精选了几道verilog常见笔试题 ,希望移知的分享能让你少走些弯路,建议收藏。

Q、Verilog task 和Verilog function有什么区别?

答案

1.function应在一个仿真时间单元内执行,task可以包含时序控制语句。

2.function无法启用task,task可以启用其他task或function。

3.function应返回一个单个值,task没有返回值。

Q使用verilog hdl实现具有同步RESET和SET的触发器,具有异步RESET和SET的触发器。

答案

Q、Verilog为什么适合描述硬件设计?

答案

always块间是并行的,符合硬件中电路并行计算的特性

always时钟触发的特性,符合寄存器的行为

Verilog是一种自顶向下的层次化设计方法,能够将复杂的大型数字系统划分为规模较小且功能相对简单的单元电路,从而加速大型数字系统的设计、调试等工作

Verilog的行为级描述方法可以简化硬件电路的设计,可借助于高级语言的精巧结构

Verilog支持开关级、门级、RTL级、算法级、系统级设计

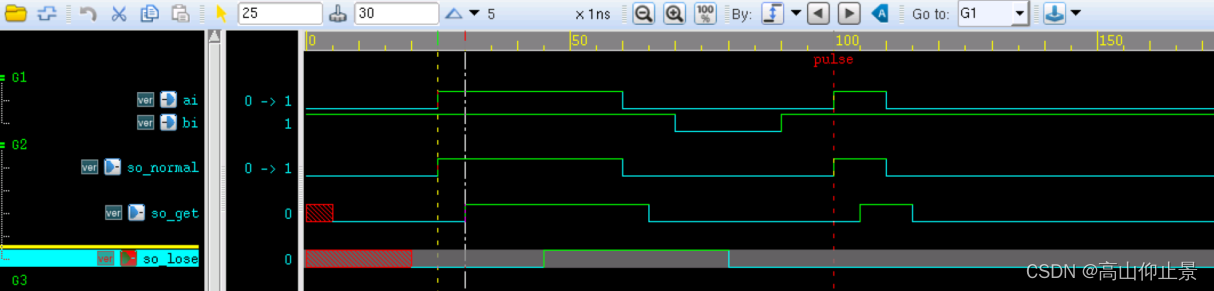

Q、Modelsim仿真步骤?

答案

vlib->vmap->vlog->vsim->run

Q、使用Verilog hdl实现2对1多路复用器。

答案

assign Y=(SEL==1’b0)?A:B;

Q、使用三态缓冲器来实现漏极开路缓冲器。

答案

assign Y=EN?DataIn:1’bz;

![[C++随笔录] vector模拟实现](https://img-blog.csdnimg.cn/9c993f624c9841b89c686e6d0e3fb6a8.png)